# **TTCrx Reference Manual**

A Timing, Trigger and Control Receiver ASIC for LHC Detectors

J. Christiansen, A. Marchioro, <u>P. Moreira</u><sup>\*</sup> and T. Toifl

CERN - EP/MIC, Geneva Switzerland

December 2005

Version 3.11

<sup>&</sup>lt;sup>\*</sup>Technical contact person e-mail: Paulo.Moreira@cern.ch

| Summary of changes                           | 7      |

|----------------------------------------------|--------|

| Version 3.11                                 | 7      |

| Version 3.10                                 |        |

| Version 3.9                                  | 7      |

| Version 3.8                                  | 7      |

| Version 3.7                                  | 7      |

| Version 3.6                                  | ′<br>7 |

| Version 3.5<br>Version 3.2                   |        |

| Version 3.0                                  |        |

| Version 2.3                                  | 8      |

| Version 2.2                                  | 8      |

| Chapter 1                                    |        |

| Introduction                                 |        |

| TTC system overview                          | 9      |

| TTCrx overview                               | 11     |

| TTCrx architecture                           |        |

| TTCrx internal registers                     | 13     |

| Chapter 2                                    | 14     |

| TTC System Frame Formats                     | 14     |

| Frame Formats                                | 14     |

| Broadcast frame                              | 14     |

| Individually-addressed commands/data frame   | 14     |

| Chapter 3                                    | 15     |

| Internal Registers                           | 15     |

| TTCrx register file                          | 15     |

| Register access via I2C bus and optical link | 16     |

| Fine Delay register 1 and 2                  | 16     |

| Coarse Delay register                        | 16     |

| Control register                             |        |

| Single bit error counter                     |        |

| Double bit and frame error counter           |        |

| SEU error counter                            |        |

| ID registers                                 |        |

| Configuration registers                      |        |

| Config 1                                     | 18     |

| Config 2                                               | 19 |

|--------------------------------------------------------|----|

| Config 3<br>Bunch counter                              | 19 |

| Event counter                                          | -  |

| Status register                                        |    |

|                                                        |    |

| Chapter 4                                              | 21 |

| Individually-Addressed Commands                        | 21 |

| TTCrx Addressing                                       | 21 |

| Individual addressing                                  | 21 |

| Global addressing with generic address 0               | 22 |

| Internal commands                                      | 22 |

| ERDUMP                                                 | 22 |

| CRDUMP                                                 | 22 |

| RESET                                                  | 23 |

| Chapter 5                                              | 24 |

| Broadcast commands                                     | 24 |

| Structure of the broadcast data packet                 |    |

| Coarse delay of the broadcast signals                  |    |

| Synchronisation with either Clock40Des1 or Clock40Des2 |    |

| Bunch and event counter reset commands                 |    |

| Chapter 6                                              | 26 |

| Loval 4 Triggar Saguanaaa                              | 26 |

| Level 1 Trigger Sequences                              |    |

| L1Accept signal                                        |    |

| ClockL1Accept signal                                   |    |

| Counter access on the BCnt<11:0> bus                   |    |

| Minimum trigger spacing                                |    |

| Trigger mode "00"                                      |    |

| Trigger mode "01"                                      |    |

| Trigger mode "10"                                      |    |

| Trigger mode "11"                                      | 29 |

| Chapter 7                                              | 30 |

| Register Access via the I2C Bus                        | 30 |

| Transferring data by using the I2C access registers    |    |

| Reading and writing register values                    |    |

| Writing to the counter registers                                |          |

|-----------------------------------------------------------------|----------|

| Writing to the status register<br>Note: Using the I2C interface | 30<br>31 |

| Chapter 8                                                       | 32       |

| Reset procedure                                                 | 32       |

| Hardwired ID and MasterMode bits                                |          |

| Minimum Width of the Reset Pulse                                |          |

| Enabling/Disabling the PROM                                     |          |

|                                                                 |          |

| PROM Data format                                                |          |

| Automatic Reset due to Watchdog circuit                         | 34       |

| Chapter 9                                                       | 35       |

| TTCrx Signals and Timing                                        | 35       |

| TTCrx external signals                                          |          |

| BCnt<11:0>                                                      | 35       |

| BCntRes                                                         |          |

| BCntStr                                                         | 36       |

| Brcst<7:6>                                                      | 36       |

| Brcst<5:2>                                                      | 36       |

| BrostStr1                                                       | 36       |

| BrcstStr2                                                       | 36       |

| Clock40                                                         |          |

| Clock40Des1                                                     |          |

| Clock40Des2<br>ClockL1Accept                                    |          |

|                                                                 |          |

| DbErrStr<br>Dout<7:0> / ID<7:0>                                 | 37       |

| DQ<3:0>                                                         |          |

| DoutStr                                                         |          |

| EvCntHStr                                                       | 27       |

| EvCntLStr                                                       | 38       |

| EvCntRes                                                        | 38       |

| In and In_b                                                     | 38       |

|                                                                 | 38       |

| JTAGTDI<br>JTAGTDO                                              | 38<br>38 |

|                                                                 |          |

|                                                                 |          |

| JTAGTRST_b<br>L1Accept                                          | 00       |

| PromClock                                                       | 38       |

| PromD                                                           | -20      |

| EnProm / PromReset                                              |          |

| Reset_b                                                         | 39       |

| SCL                                                             | 39       |

| SDA                                                             | 39       |

| Serial_B_Channel                                                | 39       |

| SinErrStr                                                       | 39       |

| SubAddr<7:0> / ID<15:8>                                         | 39       |

| TTCReady                                                        |          |

| Signal Timing                                                   | 40       |

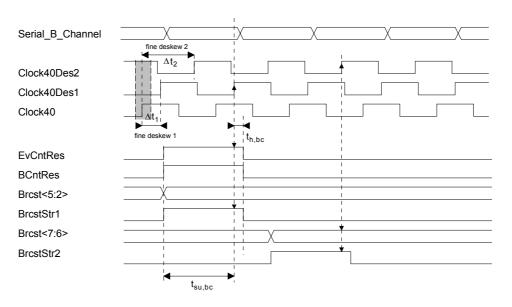

| Broadcast Command timing                     | 40 |

|----------------------------------------------|----|

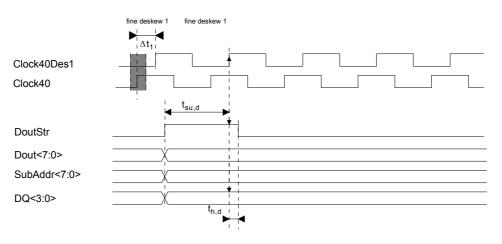

| Individually Addressed Command timing        | 41 |

| Trigger sequence                             | 41 |

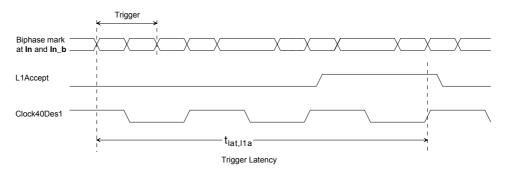

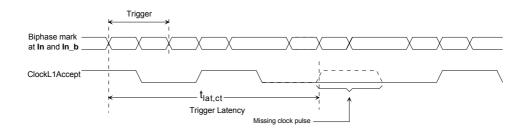

| Trigger latency                              | 42 |

| Recommended operating conditions             | 43 |

| Timing characteristics                       | 43 |

| Timing characteristics, VDD=5.0 ± 0.5 V      | 43 |

| Timing characteristics, VDD=3.3 ± 0.3 V      | 44 |

| ASIC power consumption                       | 44 |

| Chapter 10                                   | 45 |

| Radiation effects                            | 45 |

| Hamming correction machine                   | 45 |

| Watchdog circuit                             | 45 |

| Possibility of blockage in the I2C interface | 45 |

| Chapter 11                                   | 46 |

| TTCrx Packaging and Pin Assignments          | 46 |

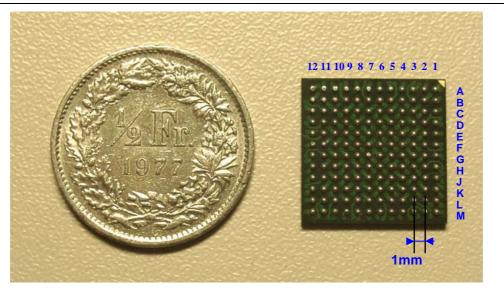

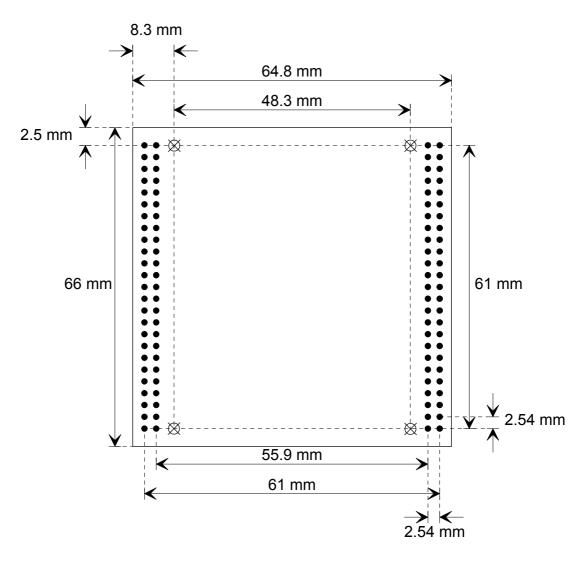

| TTCrx package                                |    |

| Pin assignments                              |    |

| Pin assignment sorted by IC bond pad number  |    |

| Pin assignments: sorted by pin               |    |

| Chapter 12                                   |    |

|                                              | •• |

| JTAG Boundary-Scan                           | 53 |

| JTAG Device ID                               | 53 |

| JTAG Valid Commands                          | 53 |

| Boundary Scan Register                       | 53 |

| Boundary scan register readout order         | 53 |

| Appendix A                                   | 55 |

| Programming Fine deskewing values            | 55 |

| Fine-Deskewing Principle                     | 55 |

| Conversion formulas                          |    |

| Conversion Table                             |    |

| Appendix B                          | 59 |

|-------------------------------------|----|

| Integrating the TTCrx in the System | 59 |

| General guidelines                  | 59 |

| Soldering Guidelines                | 60 |

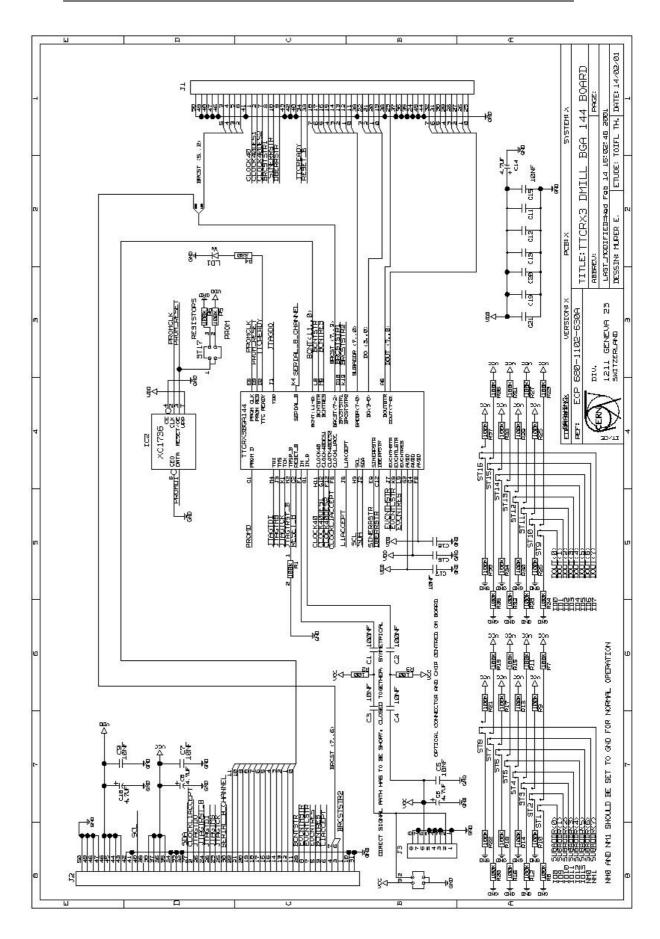

| Mezzanine Test Board                | 60 |

| Test Board Pin Assignment           | 63 |

| Connector J1                        | 63 |

| Connector J2                        | 63 |

| Appendix C                          | 64 |

| Measurement results                 | 64 |

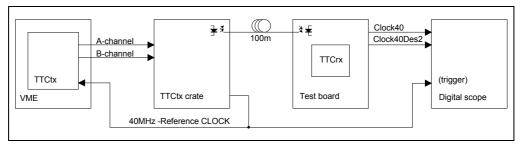

| Measurement setup                   | 64 |

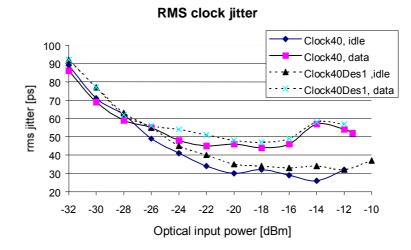

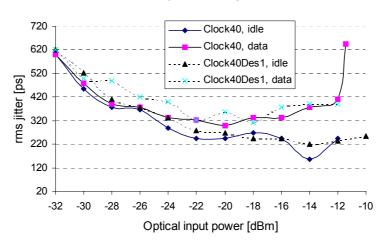

| Jitter                              | 64 |

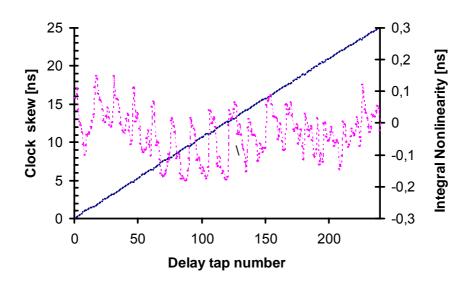

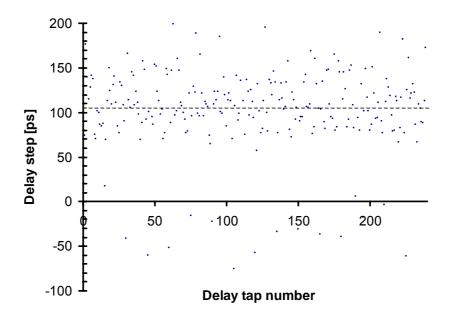

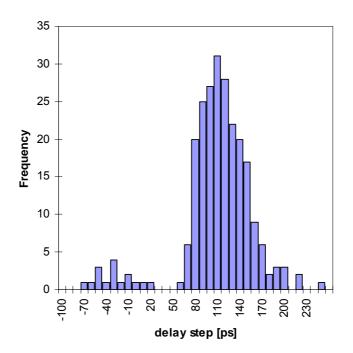

| Deskew function linearity           | 65 |

| Appendix D                          | 67 |

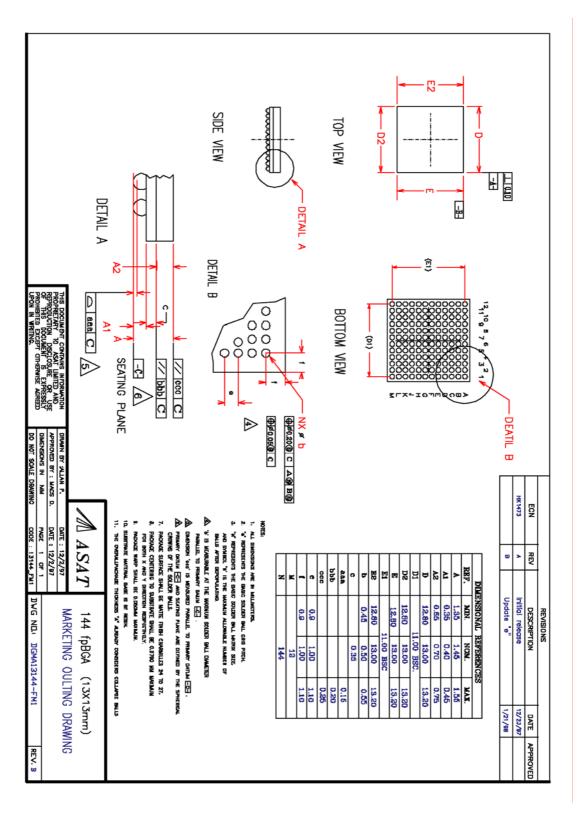

| BGA 144 mechanical data             | 67 |

| Appendix E                          | 68 |

| TTCrx known bugs                    | 68 |

| Appendix F                          | 69 |

| "Unused" CMOS inputs                | 69 |

| References                          | 70 |

## Summary of changes

#### Version 3.11

$\Rightarrow$  Paragraph concerning the action of different types of TTCrx resets added to Chapter 8.

#### Version 3.10

$\Rightarrow$  Note concerning the use of the I2C interface added to Chapter 7.

#### Version 3.9

$\Rightarrow$  Table 3 and Table 8 corrected.

#### Version 3.8

- $\Rightarrow$  Soldering Guidelines section updated.

- $\Rightarrow$  TTCrx 3.2 id number corrected (see JTAG Device ID).

- $\Rightarrow$  Section JTAG Valid Commands added.

#### Version 3.7

$\Rightarrow$  Important notice added concerning "Unused" CMOS inputs.

#### Version 3.6

- $\Rightarrow$  Introduction of a "TTCrx known bugs."

- $\Rightarrow$  Chapter 6, Level 1 Trigger Sequence extensively reviewed.

#### Version 3.5

I/O electrical information added to the manual.

#### Version 3.2

- $\Rightarrow$  New package and pin-out: 144-pin flat pack ball grid array (fpBGA).

- $\Rightarrow$  Improved immunity to Single Event Upsets (SEU).

- ⇒ Corrected bug in I2C logic. (When different chips were connected to the same I2C bus, which allowed multiple (>2) byte transfers, there was a risk of activating the I2C interface of the TTCrx although it was not actually addressed).

- $\Rightarrow$  New TTCrx mezzanine board.

- $\Rightarrow$  System integration guidelines.

- $\Rightarrow$  Soldering guidelines.

#### Version 3.0

$\Rightarrow$  Move to the radiation-hard 0.8µm DMILL technology.

- $\Rightarrow$  Extended supply voltage range (VDD: 3.3-5.0 V ± 10 %)

- $\Rightarrow$  Biasing inputs Res and Res\_b for the amplifier removed

- $\Rightarrow$  A resistor-encoded ID makes the PROM optional for applications that require radiation hardness.

- $\Rightarrow$  L1Accept trigger latency reduced by 1 cycle.

- $\Rightarrow$  I2C interface added to access internal registers.

- $\Rightarrow$  ERDUMP, CRDUMP and INIT Broadcast Commands replaced by individually-addressed commands

- $\Rightarrow$  Updated Deskewing table

- $\Rightarrow$  New pin-out

- $\Rightarrow$  New TTCrx test board

- $\Rightarrow$  Single Event Upset (SEU) Correction Logic

- $\Rightarrow$  8 bit SEU Counter

- $\Rightarrow$  Double Hamming error counter reduced to 8 bits

#### Version 2.3

$\Rightarrow$  ClockL1Accept signal trigger latency.

#### Version 2.2

- $\Rightarrow$  New TTCrx test board.

- $\Rightarrow$  Deskew mapping table.

- $\Rightarrow$  TTCrx new package Ball Grid Array.

## Introduction

The TTCrx is a custom IC that was designed by the CERN EP Microelectronics group. This document is intended to provide a functional and physical description of the TTCrx IC from the user perspective.

The TTCrx acts as an interface between the Timing Trigger and Control distribution (TTC) system for LHC detectors and its receiving end users. The ASIC delivers the clock together with control and synchronisation information to the front-end electronics controllers in the detector. The TTCrx can be programmed to compensate for particle times of flight and for propagation delays associated with the detectors and their electronics. The IC delivers the 40.08 MHz LHC clock signal, the first level trigger decision signal, and its associated bunch and event numbers. In addition, it provides for the transmission of synchronised broadcast commands and individually-addressed commands and data.

### **TTC SYSTEM OVERVIEW**

The Timing, Trigger and Control (TTC) system for LHC detectors has been specified and complete descriptions of the system and its functionality can be found in references [1] and [2]. However, a brief overview of the TTC system features that are most relevant for the understanding and utilisation of the TTCrx IC is given here.

The TTC system provides (1) all signals necessary to synchronise the detectors (the clock, event counter reset and bunch counter reset signals), (2) the level 1 trigger accept signal, and (3) arbitrary control data, which are all distributed on a single optical fibre.

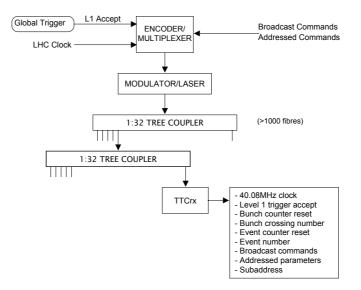

Figure 1 illustrates the basic architecture of the TTC system: at the top of the TTC tree structure, two communication channels are Time Division Multiplexed (TDM),

Figure 1 TTC optical distribution network

BiPhase Mark (BPM) encoded and transmitted over a passive optical fibre distribution network using a single laser source. One of the TDM channels (channel A) is exclusively dedicated to broadcast the first-level trigger-accept (L1A) decisions, delivering a one-bit decision for every bunch crossing. The other (channel B) is used to broadcast data to all or specific system destinations. The TTC system is also used to distribute the LHC 40.08 MHz bunch-crossing reference clock signal. This signal is not explicitly transmitted over the network and has to be recovered from the incoming data at each TTC system destination.

Data in channel B can be of two types [1], [2]: broadcast commands or individuallyaddressed commands/data. Broadcast commands are used to distribute messages to all TTC destinations in the system. When detected, these commands are executed by all the TTC receivers. The individually-addressed commands/data are implemented in the system to transmit user-defined data and commands over the network. These commands have two distinct modes of operation: in the first mode, they are aimed at the TTC receivers themselves and their user-defined content is used to control the receiver's operation. In the second mode, the data are intended for the external electronics. In this case, both the data and sub-address contents of the received commands are made externally available by the addressed TTC receiver.

Both the broadcast and the individually-addressed commands are transmitted over the TTC network using a frame format that has been specified in reference [1] and which is schematically represented in Figure 2. The frame structure contains several fields to control the transmission, and includes a field in which several redundant bits are inserted for error detection and correction. The coding scheme used is a standard Hamming code with the capability of double error detection and single bit error correction. The error correction coding covers the 8-bit data word in the case of a broadcast command/data frame and the 32-bit data in the case of an individuallyaddressed command/data frame<sup>1</sup>. The address space selection bit (E) instructs the addressed TTC receiver either to execute an internal operation or to make the received individually-addressed command/data externally available. Using this scheme it is possible to address up to 256 internal and external sub-addresses associated with up to 16K timing receivers in each timing distribution group.

| 1 | <br>1 |     |      |      |      |  |

|---|-------|-----|------|------|------|--|

| ( | START | FMT | DATA | CHCK | STOP |  |

BROADCAST COMMANDS/DATA

0 0 8b CMD/DATA 5b CHCK 1

INDIVIDUALLY-ADDRESSED COMMANDS/DATA

| 0 1 | 14b TTCrx ADDR | E | 1 | 8b SUBADDR | 8b DATA | 7b CHCK | 1 |

|-----|----------------|---|---|------------|---------|---------|---|

|-----|----------------|---|---|------------|---------|---------|---|

Figure 2 Data transmission frame format

Each frame is identified by a header bit (FMT) that indicates its type. Start (logical "0") and stop (logical "1") bits are always included at the beginning and end of the frame transmission to facilitate correct synchronisation.

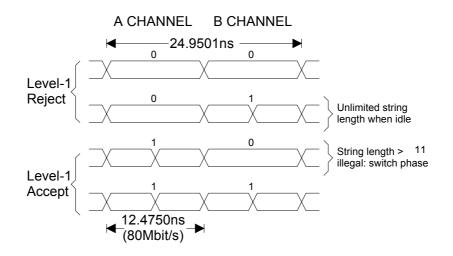

As mentioned before, channels A and B are time division multiplexed and biphase mark encoded before transmission over the network. With this type of encoding, there is a fundamental phase ambiguity between the recovered clock and the two transmitted channels. This ambiguity is resolved automatically in the receivers by monitoring a constraint imposed on the data structure in channel A: Since the number of consecutive triggers is limited, the number of consecutive "ones" in channel A is

<sup>&</sup>lt;sup>1</sup>Start, frame type and stop bits are not included in the error correction scheme.

not allowed to exceed 23 (Figure 3). There is no such limitation in channel B, so the TTCrx can identify the two channels without ambiguity.

Figure 3 TDM biphase mark encoding

### TTCrx OVERVIEW

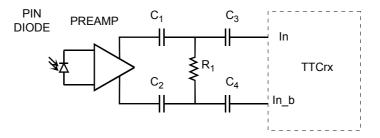

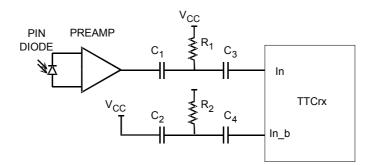

A timing receiver is associated with each of the outputs of the TTC optical distribution network. Each receiver is composed of a commercial photo-detector with integrated preamplifier and of the special purpose custom IC (TTCrx) described in this manual [3].

The TTCrx recovers and distributes the 40.08 MHz LHC reference clock with minimum jitter. Secondly, the TTCrx ASIC receives, decodes, executes and distributes the commands and data broadcast over the TTC distribution network. It recognises individually-addressed commands for purposes of internal and external control and supports the transmission of synchronised broadcast commands.

The timing receiver also delivers the first-level trigger-accept decisions and their associated bunch and event identification numbers to the detector electronics. Each TTCrx IC is identified in the distribution network by a unique 14-bit channel Identification (ID) number.

### TTCrx architecture

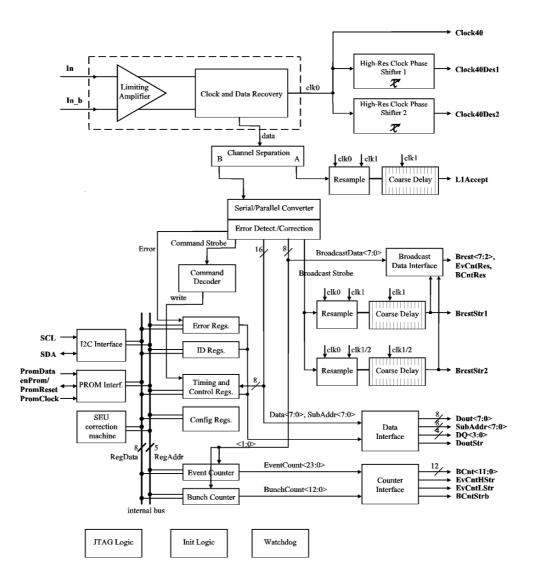

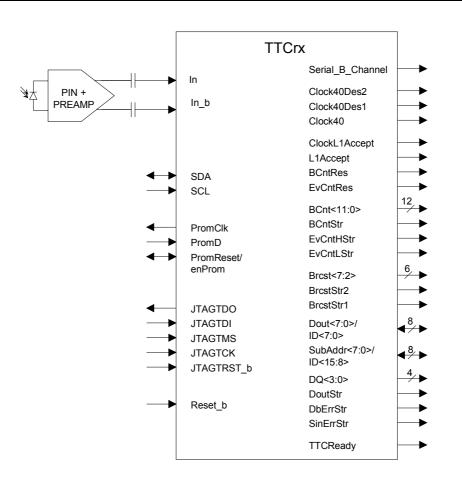

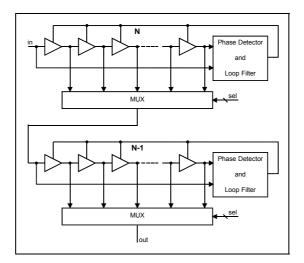

Figure 4 shows the architecture of the TTCrx. The core function of the circuit, enclosed by the dashed frame in the figure, is the recovery of the 40.08 MHz LHC clock and 80 Mbit/s serial data from a bi-phase mark encoded bit-stream, received over an optical link by a PIN-photodiode.

The differential signal coming from the photodiode<sup>2</sup> enters the chip on pins **In** and **In\_b**. A limiting amplifier then restores the signal and converts it to full swing CMOS levels. From this, the clock and data recovery circuit extracts a 40 MHz clock signal and an 80 Mbit/s data stream.

The clock signal coming directly out of the clock and data recovery circuit (clk0 in Figure 4) is fed into two independent high-resolution phase shifters, providing a programmable delay. These devices can deskew the clock signal in steps of 104ps. The two resulting de-skewed clocks are denoted **Clock40Des1** and **Clock40Des2**.

<sup>&</sup>lt;sup>2</sup> With integrated pre-amplifier

The 80 Mbit/s raw data stream is separated into two channels, denoted A and B, where channel A is exclusively reserved for the level 1 trigger accept signal, and channel B is used to transmit commands and data. Channel A is identified by the constraint that no more than 23 trigger accept decisions can occur consecutively.

Figure 4 Timing receiver block diagram

The level 1 trigger-accept signal enters a delay pipeline, which provides coarse deskewing by delaying the signal by a programmable value in steps of 25ns.

The data in channel B are fed into a serial-to-parallel converter, which decodes the two supported data formats i.e. "Broadcast Commands" and "Individually Addressed Commands". A Hamming error detection/correction unit checks the incoming data for transmission errors. For both formats, it can detect double bit errors, and correct single bit errors.

The broadcast command strobes **BrcstStr1** and **BrcstStr2**, which are validating newly received broadcast data, are coarse-delayed in two separate delay pipelines, each of a programmable length from 0 to 15.

An internal 8-bit bus connects 20 byte-wide internal registers. Three instances access this bus: the I2C interface, the PROM interface, and the Single Event Upset (SEU) error correction machine. The I2C interface allows to read and to write (or reset) all

internal registers. The PROM interface is only activated after a reset and if the PROM initialisation mode is chosen. It loads pre-defined register values, such as the chip ID number, from a serial PROM. The SEU check machine continuously monitors the registers for a radiation-induced single-event upset, thereby being able to correct single bit errors.

### **TTCrx internal registers**

The TTCrx contains several internal registers used for the control and monitoring of its operation. These registers, which are described in detail in Chapter 3, are divided in the following groups:

- Timing registers

- Control register

- Error Counters

- ID and Configuration registers

- Bunch Counter and Event Counter register

The Timing and Control registers can be written through the optical link. In addition, all registers are accessible via the I2C interface (See Chapter 7.)

The Timing registers consist of two **Fine Delay** registers, and one **Coarse Delay** register. The Fine Delay registers control the delay generated in the high-resolution phase-shifters, the Coarse Delay register controls the pipeline delay for the First Level Trigger Accept (L1A) signal and the broadcast commands. The content of the Coarse Delay register in conjunction with that of the Fine Delay register affects the total amount of de-skewing.

The **Control** register is used to select different functional modes, and to minimise the power consumption of the IC by allowing to disable some of the chip functionality in applications that do not require it. For instance, the Event and Bunch counters and the Sub-Address and Data buses can be disabled if not required by the external electronics.

The **ID** and **Configuration** registers contain the configuration bits read during initialisation. They store the 14-bit chip ID, the 6-bit I2C\_ID, parameters for the analogue part of the chip, and configuration bits to enable/disable specific blocks of the circuit for testing and debugging.

The **Bunch Counter** register contains a 12 bit wide free-running counter, incremented by the 40 MHz clock. The **Event Counter** register is 24 bit wide, and is incremented each time a level 1 trigger occurs. Both counters can be reset by specially defined broadcast commands. The Bunch counter register content is normally available to the outside logic on the **BCnt<11:0>** pins. However, during the two clock cycles following a trigger accept, the 24-bit Event Number register content can optionally be made available to the outside electronics on the same 12 output lines.

The **Single Bit Error** and the **Double Bit/Frame Error counters** are used to keep track of the number of errors occurring during data reception. Since the receiver Hamming decoder is capable of fully recovering from single bit errors, the data are accepted after correction and the Single Bit Error register incremented. When a double bit error is recognised by the receiver logic or a frame error is detected, the data are ignored and the contents of the Double Bit/Frame Error register incremented. An **SEU error counter** is incremented when a single event upset has been detected. The contents of the internal error counters are dumped on the external data bus when an error dump command is issued by the central TTC system.

## **TTC System Frame Formats**

This Chapter discusses the frame formats used for transmission of broadcast commands and Individually-Addressed Commands in the TTC system. This topic has already been introduced in section "TTC system overview" of Chapter 1.

### FRAME FORMATS

Two basic frame formats are used to transmit commands/data to the TTC receivers: Broadcast Commands (BC) and Individually-Addressed Commands (IAC). The frames are sent with several redundant bits for single bit error correction and double bit error detection. The coding scheme used is a standard Hamming code with one additional even parity bit to detect double bit errors [4]. A start and a stop bit are included in each frame for correct frame synchronisation. The two frame formats are defined as follows:

### **Broadcast frame**

The broadcast frame is used to distribute messages to all TTC receivers in the system (broadcast commands). This type of frame is identified by a "0" in its header bit (FMT). All TTCrx ASICs, after having performed appropriate checking on the received packet, execute the operation requested in the data part of the frame. For broadcast frames, error correction and detection is made on the eight data bits.

| START | FMT | CMD/DATA<br><7:0> | CHCK<br><4:0> | STOP |

|-------|-----|-------------------|---------------|------|

| 0     | 0   | ddddddd           | eeeee         | 1    |

Table 1 The structure of the Broadcast Command (BC) frame

### Individually-addressed commands/data frame

Individually-addressed commands/data frames are identified by a "1" in the header bit (FMT). This frame is used to address a single TTCrx in the system<sup>3</sup>. Data sent to a particular TTCrx are output to the **Dout<7:0>** and **SubAddr<7:0>** buses. The Data Qualifier bits **DQ<3:0>** are set to "0" for indicating IAC data, and **DoutStr** validates the data bus content. (See Chapter 9 for the signal timing.) The error correction coding covers the entire 32 data bits in the frame. Start, header and stop bits are not included in the error correction scheme.

| START | FMT | TTCrxADDR<br><13:0> | E | 1 | SUBADDR<br><7:0> | DATA<br><7:0> | CHCK<br><6:0> | STOP |

|-------|-----|---------------------|---|---|------------------|---------------|---------------|------|

| 0     | 1   | tttttttttt          | i | 1 | SSSSSSSS         | dddddd        | eeeeee        | 1    |

|       |     | tt                  |   |   |                  | d             | е             |      |

Table 2 The structure of the Individually-Addressed Command (IAC) frame

<sup>&</sup>lt;sup>3</sup>See Chapter 4 for exception on the TTCrx ADDR "0".

## **Internal Registers**

In this chapter, the TTCrx internal registers are described in detail. A brief summary of the TTCrx registers and their functionality can be found in Chapter 1.

### **TTCrx REGISTER FILE**

The TTCrx contains 20 user-accessible registers, which are listed in Table 3. The I2C register address is given in the first column, followed by the PROM sequence number, which defines the order for reading predefined values during the initialisation procedure (see Chapter 8).

| I2C<br>reg.<br>addres     | PROM<br>seq. #                         | Register name                  | Default content<br>(After reset) |  |  |  |  |  |

|---------------------------|----------------------------------------|--------------------------------|----------------------------------|--|--|--|--|--|

| S                         |                                        | Timing registers               |                                  |  |  |  |  |  |

| 0 0 Fine Delay 1 00000000 |                                        |                                |                                  |  |  |  |  |  |

| 1                         | 1                                      |                                | 00000000                         |  |  |  |  |  |

| 2                         | 2                                      | Fine Delay 2                   | 00000000                         |  |  |  |  |  |

| 2                         | Ζ                                      | Coarse Delay                   | 0000000                          |  |  |  |  |  |

| 3                         | 3                                      | Control register               | 10010011                         |  |  |  |  |  |

| >                         | 2                                      |                                | 10010011                         |  |  |  |  |  |

| 8                         |                                        | Error counter registers        | 0000000                          |  |  |  |  |  |

| 9                         | -                                      | Single error count<7:0>        |                                  |  |  |  |  |  |

|                           | -                                      | Single error count<15:8>       | 0000000                          |  |  |  |  |  |

| 10                        | -                                      | Double error count<7:0>        | 0000000                          |  |  |  |  |  |

| 11                        | 11   SEU error count <15:8>   00000000 |                                |                                  |  |  |  |  |  |

|                           | ID registers                           |                                |                                  |  |  |  |  |  |

| 16                        | 4                                      | ID<7:0>                        | 0000000                          |  |  |  |  |  |

| 17                        | 5                                      | MasterModeA<1:0>, ID<13:8>     | 0000000                          |  |  |  |  |  |

| 18                        | 6                                      | MasterModeB<1:0>, I2C_ID <5:0> | 0000000                          |  |  |  |  |  |

|                           | n                                      | Configuration registers        |                                  |  |  |  |  |  |

| 19                        | 7                                      | Config 1                       | 00011010                         |  |  |  |  |  |

| 20                        | 8                                      | Config 2                       | 10000100                         |  |  |  |  |  |

| 21                        | 9                                      | Config 3                       | 10100111                         |  |  |  |  |  |

|                           |                                        | Status register                |                                  |  |  |  |  |  |

| 22                        | -                                      | Status                         | 11100000                         |  |  |  |  |  |

|                           |                                        | Bunch counter registers        |                                  |  |  |  |  |  |

| 24                        | -                                      | Bits <7:0>                     | 0000000                          |  |  |  |  |  |

| 25                        | -                                      | Bits <15:8> 0000000            |                                  |  |  |  |  |  |

|                           |                                        | Event counter registers        |                                  |  |  |  |  |  |

| 26                        | -                                      | Bits <7:0>                     | 0000000                          |  |  |  |  |  |

| 27                        | -                                      | Bits <15:8>                    | 00000000                         |  |  |  |  |  |

| 28                        | -                                      | Bits <23:16>                   | 0000000                          |  |  |  |  |  |

Table 3 The TTCrx register file

### **Register access via I2C bus and optical link**

The I2C interface can be used to read and write (or reset) all the registers in the table. The first four registers in the table, i.e. the timing and control registers can also be written by sending individually-addressed commands on the optical link.

### Fine Delay register 1 and 2

Two deskewed clock outputs are provided by the high-resolution phase shifters of the TTCrx: **Clock40Des1** and **Clock40Des2**. The 25ns clock cycle is divided into 240 steps, equidistantly spaced by 104ps. The two fine delay registers encode the selected phase steps for the two independent clocks.

The fine delay registers are either loaded via the I2C bus or over the optical link by sending individually-addressed commands to internal sub-addresses "0" and "1" of a given TTCrx. Writing to the Fine delay registers thus allows the clock phase to be changed in steps of 104 ps between 0 and 25 ns.

Notice that due to the architecture of the phase shifter circuit, the byte-value of a Fine Delay register is not proportional to its corresponding phase delay, but has to be encoded first. Formulas and tables for encoding delay values are given in Appendix A.

### **Coarse Delay register**

As shown in Figure 4, the TTCrx contains several coarse delay pipelines, providing the programmable delay of the Level 1 Trigger Accept and broadcast command signals in steps of 25ns. The Coarse Delay register holds the delay parameters for these signals. The content of this register in conjunction with that of the Fine Delay registers thus affects the total amount of deskewing.

The eight-bit **coarse delay** register holds two sets of four bits. Each determining the coarse deskewing in a range of [0:15] for two groups of registers: The Coarse delay register bits <3:0> control the amount of deskewing applied to the **L1Accept**, **BrcstStr1**, **BcntRes**, **EvCntRes**, **Brcst<5:2>** signals, whereas bits <7:4> determine the deskewing of the signals **BrcstStr2** and **Brcst<7:6>**.

Since the same deskewing is applied to both the L1A signal and the bunch/event counter reset strobes, the deskewing of the latter ones will also have to be performed at the source of the TTC system to compensate for the time necessary to transmit and decode these commands.

| Bits  | Name           | Affected signals                                      |

|-------|----------------|-------------------------------------------------------|

| <3:0> | Coarse delay 1 | L1Accept, BrcstStr1, BcntRes,<br>EvCntRes, Brcst<5:2> |

| <7:4> | Coarse delay 2 | BrcstStr2, Brcst<7:6>.                                |

### **Control register**

The Control register is used to select the operational mode of the circuit, and to minimise the IC power consumption by allowing the disabling of some of the chip functionality in applications that do not require it. The bits of the **Control register** are allocated as follows (see Table 5):

Bits 0 and 1 specify the mode of operation for the bunch and the event counter. After the reception of a level 1 trigger accept signal, a trigger sequence is started, in which the contents of the different counters are multiplexed on the **BCnt<11:0>** bus. The settings of the control register specify the type of this trigger sequence, as described in detail in Chapter 6.

Bit 2 of the Control register ("SelClock40Des2") determines if **Clock40Des1** or **Clock40Des2** is used for the synchronisation of the **BrcstStr2** signal and the associated upper two bits of the broadcast command byte **Brcst<7:6>**.

Bits 3 to 7 enable or disable various output signals. Switching off signals not in use significantly reduces the power consumption of the circuit.

|   | Function                       | Reset state |

|---|--------------------------------|-------------|

| 0 | Enable Bunch Counter operation | 1           |

| 1 | Enable Event Counter operation | 1           |

| 2 | SelClock40Des2                 | 0           |

| 3 | Enable Clock40Des2 output      | 0           |

| 4 | Enable ClockL1Accept output    | 1           |

| 5 | Enable Parallel output bus⁴    | 0           |

| 6 | Enable Serial B output         | 0           |

| 7 | Enable (non-deskewed) Clock40  | 1           |

|   | output                         |             |

Table 5 Bit assignment of the Control register.

#### Single bit error counter

This 16-bit counter keeps track of the number of single bit errors recognised by the receiver's Hamming decoder. Since these errors are fully corrected, received commands and data are accepted by the TTCrx after correction by the receiver.

#### Double bit and frame error counter

This 8-bit counter counts the number of double bit Hamming errors and frame errors (i.e. received stop bit not equal to one). After such an error, the received data are ignored and no action is taken. The TTCrx tries to resynchronise to the next start bit. In the process of resynchronisation, errors can again occur.<sup>5</sup>

#### **SEU error counter**

The four timing and control registers, the three ID registers and the three Configuration registers are protected against the effect of a single event upset (SEU) by using a Hamming check sum. A SEU correction-machine continuously scans the contents of the registers and corrects them in the case that a single-event upset has occurred due to irradiation. Upon detection of an error, an automatic correction is performed by which the 8-bit SEU error counter is incremented.

#### **ID** registers

There are two different ID values occupying a total of three locations in the register file: The 14 bit chip ID, which is used for identifying Individually-Addressed

<sup>&</sup>lt;sup>4</sup> Setting this bit enables the following output pins: Dout<7:0>, DQ<3:0>, SubAddr<7:0> and DoutStr. All the other outputs function normally.

<sup>&</sup>lt;sup>5</sup> Note that both the single error counter and double bit and frame error counter are disabled once their contents reach 65535 and 256, respectively. A re-initialisation sequence is necessary to reactivate and reset these counters.

Commands (IAC) sent over the optical link, and the 6 bit wide I2C\_ID, serving as a base address for accessing the chip via the I2C interface. The bit assignment of the three ID registers is shown in Table 6.

After a reset (Chapter 8), the ID register latches the values on the SubAddr<7:0>, Data<7:0> buses in the 16 bit ID register, and the values of {SubAddr<7:6>, Data<5:0>} in the 8 bit wide I2C\_ID register. By this, after a reset, the 6-bit I2C base address is then identical to the lowest six bits of the 14-bit chip ID. If the serial PROM is used for initialisation, these values are overwritten by the contents of the PROM.

| Bit # | Name        | Function                | Init value<br>Pin name | Change<br>allowed? |

|-------|-------------|-------------------------|------------------------|--------------------|

|       |             | ID<7:0>                 |                        |                    |

| <7:0> | ID<7:0>     | Chip ID (lower<br>bits) | Dout<7:0>              | YES                |

|       |             | ID<15:8>                |                        |                    |

| <5:0> | ID<13:8>    | Chip ID (upper<br>bits) | SubAddr<5:0>           | YES                |

| <7:6> | MMA<1:0>    | MasterModeA<1:0         | SubAddr<7:6>           | NO                 |

|       | ID_I2C      |                         |                        |                    |

| <5:0> | ID_12C<5:0> | I2C base address        | Dout<5:0>              | YES                |

| <7:6> | MMB<1:0>    | MasterModeB<1:0         | SubAddr<7:6>           | NO                 |

Table 6 Bit assignments of the three ID registers.

The upper two bits of the ID register (bits <15:14>) and the upper two bits of the ID\_I2C register (bits <7:6>) have a special meaning: They are not part of the identification number, but constitute two "master mode" bits, MasterModeA<1:0> and MasterModeB<1:0>, which determine the overall operational mode of the circuit. By hard-wiring their values via resistors, these two bits are guaranteed to be set to the correct value after a reset without the need for a radiation-hard PROM. They are replicated (MMA=MMB) for redundancy, in order to avoid that the chip, due to a single event upset (SEU), can get stuck in a mode where it could not get back to normal operation. The function of the master mode bits is explained in Chapter 8.

### **Configuration registers**

In order to be able to test the circuit and to fine-tune certain parameters, three configuration registers are implemented on the circuit, denoted "Config1-3". The following tables give an overview of the bit assignment of these registers. **Most bits are reserved for testing and debugging purposes, and are not supposed to be changed by the user.** Only the register bits that can be changed by the user are described in more detail.

#### Config 1

The bit allocation of the Config 1 register is displayed in the table below:

|       | Config 1 (Reg.Adr. 19) |                                           |                  |                    |  |

|-------|------------------------|-------------------------------------------|------------------|--------------------|--|

| Bit # | Name                   | Function                                  | Default<br>value | Change<br>allowed? |  |

| <2:0> | dll_isel<2:0>          | Selects DLL current                       | 010              | YES                |  |

| <5:3> | pll_isel<2:0>          | Selects PLL current                       | 011              | YES                |  |

| 6     | dll_sel_aux_1          | Selects test input for<br>phase shifter 1 | 0                | NO                 |  |

| 7 | dll_sel_aux_2 | Selects test input for | 0 | NO |

|---|---------------|------------------------|---|----|

|   |               | phase shifter 2        |   |    |

Table 7 Bit assignment of Configuration register 1

The lower three bits, "dll\_isel<2:0>" specify the charge-pumps current used in the delay-locked loops (DLLs) of the high-resolution phase shifters. Lower values, in general, lead to lower jitter on the clock lines. "pll\_isel<2:0>" specifies the charge-pump current for the phase-locked-loop (PLL), which provides the function of clock recovery. Also in this case, lower values in general result in lower jitter. There are cases, however, e.g. when the transmitted data are highly random, in which jitter can be minimised by using higher values.

#### Config 2

"cf\_en\_check\_machineA" of the Config 2 register (see Table 8) enables the internal Hamming check-machine, which constantly scans the internal registers and corrects them in case of a single event upset (SEU). For redundancy, the Config 3 register (see Table 9) contains a second bit with the same function, denoted "cf\_en\_check\_machineB". For switching off the Hamming check machine, both bits have to be zero.

|       | Config 2 (Reg.Adr. 20)   |                                                                       |                  |                    |

|-------|--------------------------|-----------------------------------------------------------------------|------------------|--------------------|

| Bit # | Name                     | Function                                                              | Default<br>value | Change<br>allowed? |

| <2:0> | mux_select<2:0           | Selects test outputs (see detailed map below)                         | 101              | NO                 |

| 3     | cf_sel_test_PD           | Selects external test signal for enabling the PLL phase detector.     | 0                | NO                 |

| 4     | cf_sel_inputA            | When 0 selects inputs<br>from optical link,<br>otherwise test_in<3,4> | 0                | NO                 |

| 5     | cf_PLL_aux_<br>reset     | Assert PLL test reset line                                            | 0                | NO                 |

| 6     | cf_DLL_aux_<br>reset     | Assert DLL test reset line                                            | 0                | NO                 |

| 7     | cf_en_check_<br>machineA | Enables Hamming check<br>machine                                      | 1                | YES                |

Table 8. Bit assignment of Configuration register 2

#### Config 3

|       | Config 3 (Reg. adr. 21)     |                                                                                           |                  |                    |

|-------|-----------------------------|-------------------------------------------------------------------------------------------|------------------|--------------------|

| Bit # | Name                        | Function                                                                                  | Default<br>value | Change<br>allowed? |

| <2:0> | frequ_check_<br>period<2:0> | Stop frequency detection<br>phase after 2^(n+4) cycles<br>without "frequ_low"<br>detected | 111              | NO                 |

| 3     | cf_dis_INITfaster           | If 1 disables automatic<br>frequ. increase after PLL<br>reset                             | 0                | NO                 |

| 4     | cf_dis_watchdog             | If 1 disables watchdog<br>circuit                                                         | 0                | NO                 |

| 5 | cf_en_Hamming            | Enables Hamming error<br>detection/correction on<br>incoming data stream | 1 | NO  |

|---|--------------------------|--------------------------------------------------------------------------|---|-----|

| 6 | cf_en_testlO             | Enables Test<br>Input/Outputs                                            | 0 | NO  |

| 7 | cf_en_check_<br>machineB | Enables Hamming check<br>machine                                         | 1 | YES |

Table 9 Bit assignment of Configuration register 3

#### **Bunch counter**

The bunch counter is incremented by the received clock signal. This counter is 12 bit wide and is reset by sending a BCRST broadcast command, by writing to the register via the I2C interface, and by the chip initialisation procedure.

#### **Event counter**

The event counter is incremented upon reception of a trigger accept signal in channel A. This counter is 24 bit wide and is reset by sending an ECRST broadcast command, by writing to the register via the I2C interface, and by the chip initialisation procedure.

#### **Status register**

The status register allows to monitor some internal signals crucial for the operation of the circuit.

|       | Status (Reg. adr. 22) |                                                                                                             |                  |  |

|-------|-----------------------|-------------------------------------------------------------------------------------------------------------|------------------|--|

| Bit # | Name                  | Function                                                                                                    | Default<br>value |  |

| <3:0> | -                     | Always zero                                                                                                 | 0000             |  |

| 4     | auto_reset_flag       | A 1 indicates that an automatic reset<br>has occurred due to a timeout<br>condition in the watchdog circuit | 0                |  |

| 5     | frame_synch           | A 1 indicates that channel B is synchronized to the data stream                                             | 1                |  |

| 6     | dll_ready             | A 1 indicates that the High-Resolution phase shifters are working properly                                  | 1                |  |

| 7     | pll_ready             | A 1 indicates that the clock and data recovery circuit is locked on the incoming data stream                | 1                |  |

During normal operation, bits <5:7> have to be one. If this is not the case, then, either the chip was reset or an error has occurred.

The status register cannot be written like an ordinary register since it does not contain any memory elements. A write access to this register has a special function, which is described in Chapter 7.

## Individually-Addressed Commands

As already described in the introduction, the TTCrx chip recognises two different data formats, broadcast commands and individually-addressed commands. Broadcast commands are decoded by all TTCrx's, whereas individually addressed commands are sent to specific chips with a certain identification number (ID).

This chapter discusses the "Individually-Addressed Command" (IAC) format, where a message is sent to a specific TTCrx in the system, identified by a 14-bit ID number. The net data contained in the IAC packet amounts to 16 bits. It is divided into an 8-bit DATA byte, and an 8-bit SUBADDR byte.

Individually-addressed commands can be sent to the outside world, such that their net 16-bit data content appears on the **Dout<7:0>** and **SubAddr<7:0>** pins and **DoutStr** validates the signal. Secondly, IACs can be used to write internal registers of the TTCrx and execute internal commands. One bit in the IAC data frame (the "E" bit in Table 2) signals if the command is internal or external.

### TTCRX ADDRESSING

Each TTCrx IC is identified in the distribution network by a unique 14-bit channel Identification (ID) number. This number is read during the reset procedure (see Chapter 8), either from a serial PROM or - by using the hard-wired ID mechanism - from the **ID<15:0>** bus (which shares its pins with the **SubAddr<7:0>**, **Dout<7:0>** bus).

#### Individual addressing

The individually addressable space for each TTCrx is split into two: internal and external. The internal address space is used to write the TTCrx internal registers, while the external space allows commands and data to be transmitted to the detector electronics. When an individually-addressed command/data frame is received with the E bit equal to "0" the *internal* address space is assumed. A "1" received in the E bit indicates *external* addressing. Upon reception of an external command, the sub-address and data buses are set according to the data contents of the received command.

| SUBADDR <7:0> | Register / Command          |

|---------------|-----------------------------|

| 00000000      | Fine Delay Register 1 <7:0> |

| 0000001       | Fine Delay Register 2 <7:0> |

| 0000010       | Coarse Delay Register <7:0> |

| 00000011      | Control Register <7:0>      |

| 00000100      | Execute ERDUMP command      |

| 00000101      | Execute CRDUMP command      |

| 00000110      | Execute RESET command       |

The TTCrx internal addressing space is allocated as follows:

Hence, some sub-addresses (0-3) are used for writing register values, whereas others (4,5,6) are used for executing internal commands. In the first case, the 8 bit DATA section of the IAC frame is written in the specified register, while in the second case the content of the DATA section is ignored. The function of the commands is explained later in this chapter.

#### Global addressing with generic address 0

If an individually-addressed command is to be received by all connected TTCrx's in a system, disregarding the individual values of their IDs, the command can be sent to the generic address 0.

Note that in this case IACs are similar to broadcast commands, with the difference that the net data content of the frame is 16 bits. Although the concept of *individually* addressed commands, of course, does not apply any more in the strict sense of the word, this feature is useful for programming internal register values for the whole system with a single transmission.

### **INTERNAL COMMANDS**

This section describes the internal commands that can be executed by the TTCrx. The commands are issued by sending an internal individually-addressed command (IAC) as described above.

#### **ERDUMP**

**Error dump** (Sub-address = 4): the internal error counters are dumped on the external data bus **Dout<7:0>**. Data are output during four consecutive clock cycles. As for a normal data transfer, the data strobe line **DoutStr** signals the presence of valid data on the bus and the **DQ<3:0>** bits indicate the type of the data according to the following table:

| DQ<3:0 | Data<7:0> bus content         |

|--------|-------------------------------|

| >      |                               |

| 0001   | Single Bit Error Counter Low  |

| 0010   | Single Bit Error Counter High |

| 0011   | Double Bit Error Counter Low  |

| 0100   | SEU Error Counter             |

#### CRDUMP

**Configuration register dump** (Sub-address = 5): The internal configuration and control registers are dumped on the external data bus. For this operation the data qualifier bits are used as follows:

| DQ<3:0 | Data<7:0> bus content |

|--------|-----------------------|

| >      |                       |

| 0101   | Fine Delay register 1 |

| 0110   | Fine Delay register 2 |

| 0111   | Coarse Delay register |

| 1000   | Control register      |

| 1001   | ID register <7:0>     |

| 1010   | ID register <13:8>    |

### RESET

#### **Reset the TTCrx** (Sub-address = 6)

This instruction initiates a complete reset procedure (see Chapter 8) of the TTCrx. It should therefore be used with care. The command can only be received, of course, if the clock-and data recovery circuit of the TTCrx is working correctly.

## **Broadcast commands**

#### Structure of the broadcast data packet

The TTCrx can receive up to 256 different broadcast messages, encoded in the 8-bit broadcast data packet. These 8 bits are divided into three groups: the two lowermost bits, the four middle bits, and the two uppermost bits. The lowermost bits <1:0> are reserved for the bunch counter reset signal (bit 0), and the event counter reset signal (bit 1), the middle four bits <5:2> are referred to as the **system** broadcast message, the uppermost bits <7:6> as the **user** broadcast message. An overview of the broadcast data packet is given in the table below. (The details about timing and synchronising clock are explained later in this chapter.)

| Bit # | Signal name            | Internal action<br>when high     | Coarse delay<br>value<br>1=bits<3:0><br>2=bits<7:4> | Output syn-<br>chronised<br>ith<br>1:<br>Clock40Des1<br>2:<br>Clock40Des2 | Output pin<br>name |

|-------|------------------------|----------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------|--------------------|

| 0     | Bunch counter<br>reset | Resets internal<br>bunch counter | 1                                                   | 1                                                                         | BcntRes            |

| 1     | Event counter<br>reset | Resets internal<br>event counter | 1                                                   | 1                                                                         | EvCntRes           |

| <5:2> | System<br>message      | -                                | 1                                                   | 1                                                                         | Brcst<5:2>         |

| <7:6> | User message           | -                                | 2                                                   | 1 or 2                                                                    | Brcst <7:6>        |

The broadcast data are accessible at the outside in the form of the event and bunch counter reset strobes (**BCntRes** and **EvCntRes**), corresponding to bits <1:0> of the broadcast data byte sent, and of the broadcast data bus **Brcst<7:2>**, which is validated by the strobe signals **BrcstStr1** and **BrcstStr2**.

It has to be noted that **BcntRes** and **EvCntRes**, although in principle corresponding to Brcst<1:0>, actually function as strobe signals, i.e. they stay high for only one cycle. On the other hand, data sent in bits <7:2> will remain active on **Brcst<7:2>** until the next broadcast command is sent.

### Coarse delay of the broadcast signals

The different parts of the broadcast message can be delayed in steps of 25ns. The following rules apply: Bits <5:0> of the broadcast message (thus including the reset strobes for the event and bunch counter and the system messages) are delayed by the value defined by bits <3:0> of the Coarse Delay register, whereas the user message bits <7:6> are delayed by a value stored in bits <7:4> of the Coarse Delay register. It should be noted that the broadcast message bits <5:2> are thus delayed by the same value as the L1Accept signal.

The delays affect both the strobe signals (**BrcstStr1**, **Brcstr2**) and the data signals (**Brcst<7:2>**, **EvCntRes**, **BcntRes**).

### Synchronisation with either Clock40Des1 or Clock40Des2

Bits <5:0> of the broadcast data are always synchronised to **Clock40Des1**, whereas the bits of the *user* broadcast message (bits <7:6>) can be synchronised to either **Clock40Des1** or **Clock40Des2**, depending on Bit 2 ("SelClock40Des2") of the Control register. Hence, the strobe signals **BrcstStr1** and the lower data bits (**BcntRes, EvCntRes, Brcst<5:2>**) are always synchronised to **Clock40Des1**, whereas **BrcstStr2** and **Brcst<7:6>** are synchronised to either **Clock40Des1** or **Clock40Des2**.

#### Bunch and event counter reset commands

As described above, the function of the two lowest bits of the broadcast byte is predefined in the TTC system: Bit 0 carries the bunch counter reset signal, and bit 1 the event counter reset signal, corresponding to the following command table:

| Command | Format    | Function                       |  |

|---------|-----------|--------------------------------|--|

|         | uu ssssss |                                |  |

| NOP     | uu ssss00 | Do nothing                     |  |

| BCRST   | uu ssss01 | Bunch counter reset            |  |

| ECRST   | uu ssss10 | Event counter reset            |  |

| EBCRST  | uu ssss11 | Reset event and bunch counters |  |

Table 10 Pre-defined broadcast commands

Note that sending a Bunch counter reset or an Event counter reset signal also resets the internal bunch or event counter of the TTCrx. The interpretation of the upper six bits in the broadcast data byte (two **user** and four **system** bits) is left to the user.

## Level 1 Trigger Sequences

### L1Accept signal

After receiving an L1Accept signal on channel "A", the TTCrx activates the **L1Accept** pin after a delay specified by the lower four bits of the Coarse Delay Register.

### ClockL1Accept signal

The **ClockL1Accept** signal combines the **Clock40** signal with the trigger information: Upon reception of a trigger accept, the output is suppressed during one clock cycle. **ClockL1Accept** has lower trigger latency than **L1Accept**. But, unlike the latter, its phase is not programmable. In order to save power, it is possible to disable the **ClockL1Accept** signal by clearing Bit 4 of the Control register.

#### Counter access on the BCnt<11:0> bus

The 12-bit Bunch and the 24-bit Event counter values are multiplexed on the **BCnt<11:0>** counter output bus. The lowest two bits in the Control register determine what signals are available on **BCnt<11:0>** during a trigger sequence according to the following table:

| Control Register,<br>bit <1:0> | Trigge<br>r Cycle | Signal on<br>BCnt<11:0> pins | Strobe signal |

|--------------------------------|-------------------|------------------------------|---------------|

| 00                             | default           | Event counter low            | -             |

|                                | 0                 | Event counter low            | EvCntLStr     |

| 01                             | default           | Bunch counter                | -             |

|                                | 0                 | Bunch counter                | BCntStr       |

| 10                             | default           | Event counter low            | -             |

|                                | 0                 | Event counter low            | EvCntLStr     |

|                                | 1                 | Event counter high           | EvCntHStr     |

| 11                             | default           | Event counter low            | -             |

|                                | 0                 | Bunch counter                | BCntStr       |

|                                | 1                 | Event counter low            | EvCntLStr     |

|                                | 2                 | Event counter high           | EvCntHStr     |

Table 11 Bunch counter bus trigger cycles.

Trigger cycle 0 is the cycle during which, after the specified coarse delay, the **L1Accept** signal is activated. Cycles 1 and 2 are the following two consecutive cycles.

The 'default' value in the table corresponds to the case that no trigger sequence is active. Although the specified signal is available on the **BCnt<11:0>** bus, none of the strobe signals (**BCntStr**, **EvCntLStr**, **EvCntHStr**) is activated.

Note that if bits <1:0> of the Control Register are set to '01' then **BCnt<11:0>** is constantly changing, leading to higher power consumption.

The first event after an Event Counter Reset (**ECRST** or **EBCRST**) will be marked as event number zero.

### Minimum trigger spacing

The minimum allowed trigger spacing, that is, the maximum trigger rate, depends on the programmed trigger mode (see Table 11).

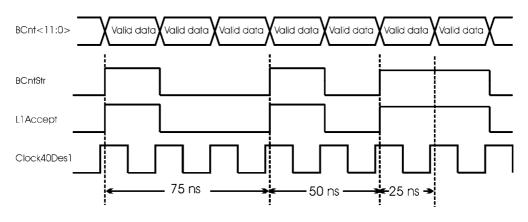

### Trigger mode "00"

In trigger mode "00", upon the reception of an L1 accept signal on channel "A", the TTCrx makes available on the bunch counter bus the content of the event counter low register.

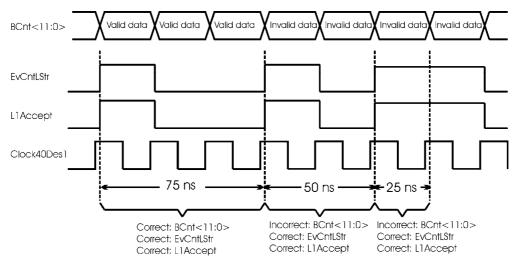

This mode has been specified to support a minimum trigger spacing of one (that is, a maximum trigger rate of 40 MHz). However, <u>if the trigger spacing is decreased to less than three, the bunch counter bus content becomes erroneous, although the **L1Accept** and **EvCntLStr** signals continue to operate correctly (see Figure 5). Consequently, if the bunch counter bus content is used in the system, the minimum trigger spacing becomes limited to 3. If only signals **L1Accept** and **EvCntLStr** are used, then a minimum trigger spacing of one is still valid. Due to the channel identification constraint (see TTC system overview) the maximum number of consecutive triggers allowed is 11.</u>

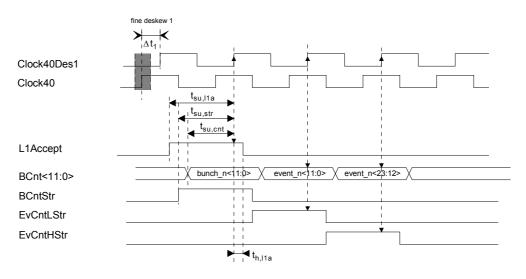

Figure 5 Trigger mode "00"

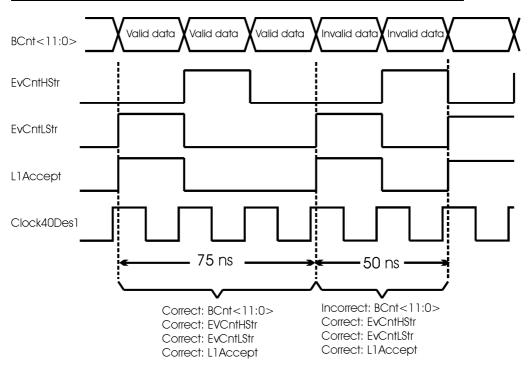

### Trigger mode "01"

In this mode the minimum trigger spacing is one. That means that consecutive L1 accepts can be received in channel "A" resulting in a maximum trigger rate of 40 MHz. Due to the channel identification constraint (see TTC system overview) the maximum number of consecutive triggers allowed is 11. This mode works as specified under all conditions. See Figure 6 for an example of operation.

#### **RD12** project collaboration

Figure 6 Trigger mode "01"

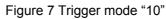

### Trigger mode "10"

In trigger mode "10", upon the reception of an L1 accept signal on channel "A", the TTCrx makes available on the bunch counter bus the content of the event counter low followed by the content of the event counter high register.

This mode has been specified to support a minimum trigger spacing of two (that is, a maximum trigger rate of 20 MHz). However, <u>if the trigger spacing is decreased to</u> two, the bunch counter bus content becomes erroneous (see Figure 7). Nonetheless, the **L1Accept**, **EvCntLStr and EvCntHStr** signals continue to operate correctly (see Figure 7). Consequently, if the bunch counter bus content is used in the system, the minimum trigger spacing becomes limited to 3. If only signals **L1Accept**, **EvCntLStr** and **EvCntHStr** are used, then a minimum trigger spacing of two is still valid.

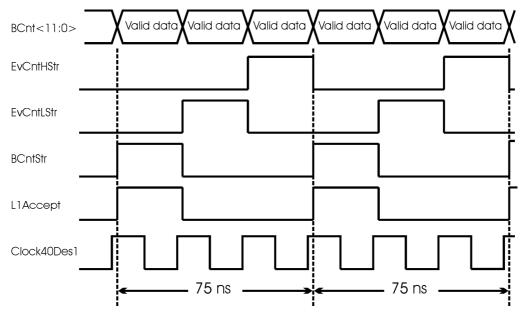

### Trigger mode "11"

This is the default TTCrx trigger mode. In this mode, the minimum trigger spacing is three. That means that at least two L1 rejects must exist between two L1 accepts, resulting in a maximum trigger rate of 13.33 MHz. After the reception of an L1 accept on channel "A", the TTCrx will output sequentially on the "Bunch Counter Bus", the "Bunch Counter" content followed by the contents of the "Event Counter Low" and "Event Counter High" registers. This mode works as specified under all conditions. See Figure 8 for an example of operation.

Figure 8 Trigger mode "11"

## **Register Access via the I2C Bus**

The I2C bus protocol defines a standard for an asynchronous serial bus with a maximum transfer rate of 1 Mbit/s [7].

### Transferring data by using the I2C access registers

All data transfer over the I2C bus is performed using only two registers: The **I2C\_pointer** register and the **I2C\_data** register. The **I2C\_pointer** register is five bits wide and contains the address of the internal register as defined in Table 3 (page 16). When reading the **I2C\_data** register, the content of the TTCrx register *being* addressed by the pointer register is transferred. Conversely, writing a byte to the **I2C\_data** register in fact writes to the TTCrx register *addressed by* the **I2C\_pointer** register. Hence, each I2C access is performed in two steps:

- 1) Write the register number in the **I2C\_pointer** register

- 2) Read or write the **I2C\_data** register

According to the I2C bus specification, each device on the bus is addressed by a 7-bit wide I2C device address. Each TTCrx chip occupies two consecutive positions in the 7-bit I2C address space. Hence, it is possible to address 64 devices in the system. The 7-bit I2C address is derived from the content of the ID\_I2C<5:0> base address register in the following way:

| I2C access<br>register name | Resulting 7 bit<br>I2C address |

|-----------------------------|--------------------------------|

| I2C_pointer                 | ID_I2C<5:0> * 2                |

| I2C_data                    | ID_I2C<5:0> * 2 + 1            |

| ress calculation. |

|-------------------|

| ress calculation. |

#### Reading and writing register values

All the registers shown in Table 3 (page 16) can be accessed over the I2C bus. After a write access, the corresponding register is in general set to the value of the transmitted data byte. However, a write access on some special registers i.e. the counter registers and the status register, has a different meaning:

#### Writing to the counter registers

Any write access to one of the counter registers (error counters, bunch counter, event counter) resets the respective counter.

#### Writing to the status register

Writing the value 5 to the status register initiates a reset procedure.

Writing the value 0 the status register deletes the watchdog-reset flag (See also Chapter 8).

#### Note: Using the I2C interface

Please note that correct operation of the I2C bus requires the TTCrx to be locked to the TTC signal ("TTC Ready").

## **Reset procedure**

A reset initialises fully or partially the TTCrx, and can be initiated either

- a) By a low on the **Reset\_b** pin;

- b) By sending an (individually-addressed) RESET command via the optical link;

- c) By sending a reset command on the I2C interface;

- d) By a timeout condition in the watchdog circuit.

The full chip is initialized by a logic "0" (low level) on the reset pin. Any other type of reset (individually-addressed RESET command, I2C RESET command and watchdog timeout condition) initializes all the registers with the exception of the user registers (Fine Delay 1 and 2, Coarse Delay and the Control register).

#### Hardwired ID and MasterMode bits

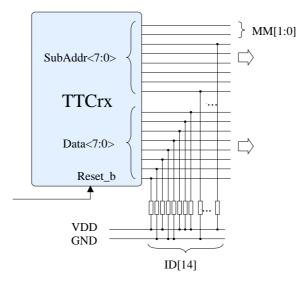

This section describes how, after a reset, the TTCrx reads in the value of its ID, encoded with connected resistors, as seen in Figure 9.

During a reset, the output drivers on the **SubAddr<7:0>, Data<7:0>** buses are deactivated. Resistors, which connect the different pins of the bus to either VDD or GND, encode a 16 bit value, which pull the values on **SubAddr<7:0>, Data<7:0>** to a logic zero or one.

This number is then latched at the rising edge of the **Reset\_b** signal. After the latching, the output drivers are switched on again, and **SubAddr<7:0>**, **Data<7:0>** act as outputs.

By this, the serial PROM, which was the unique option to set the chip ID in early versions, is not necessary any more. Initialising the chip with a PROM, which is still supported as an option, can however be useful to fine-tune certain chip parameters, whose predefined values were set conservatively. (e.g. the currents used in the DLLs and the PLL). Since the definition of the configuration registers has changed, it is not possible to transfer any programmed PROM from previous versions.

Figure 9 Using the SubAddr<7:0> and Data<7:0> bus for reading the 14-bit chip ID and the two MasterMode<1:0> bits after a reset

The two uppermost bits of **SubAddr<7:0>** are not used for the ID. They define the "MasterMode<1:0>" bits. These bits are crucial for the operation of the TTCrx, since they encode the basic mode of operation, and were therefore included in the hard-wired initialisation procedure.

The function of the **MasterMode<1:0>** bits is described in the following table:

| Bit # | Pin        | Function                                 | default<br>value |

|-------|------------|------------------------------------------|------------------|

| 0     | SubAddr<6> | Disable Serial/Parallel Converter when 1 | 0                |

| 1     | SubAddr<7> | Test Mode when 1                         | 0                |

Table 13 Definition of the two MasterMode bits. They are read in after a reset from SubAddr<7:6>.

Master mode bit 0 determines if serial/parallel conversion shall be performed on the data in channel B. For applications where the TTCrx is to be used solely as a serial receiver, all the internal command decoding can hence be switched off by setting this bit to one.

Master mode bit 1 enables the test/debugging mode, which is never used during normal operation.

For choosing the standard mode of operation, SubAddr<6> and <7> must be resistor-connected to GND.

#### Minimum Width of the Reset Pulse

If the hardwired ID option is used, the external reset pulse has to have a minimum duration such that the resistors can safely pull the voltage to the desired level. Let R be the value of the pull-up / pull-down resistor, and C the overall capacitance on a pin, then the reset pulse should have a minimum width of

$$t_{\min} = 10 \cdot R \cdot C$$

.

For example, values of  $R = 100 \text{ k}\Omega$  and C = 50 pF result in a minimum width of the reset pulse of 50 µs. Smaller values of *R* lead to smaller minimum reset pulses, but at the same time increase the static current consumption in the resistors after the reset.

### **Enabling/Disabling the PROM**

In the case that a serial PROM<sup>6</sup> is used to set the chip ID and other register contents, the value read from the **SubAddr<7:0>**, **Data<7:0>** bus is overwritten by the PROM content.

In order to signal that a PROM should be used to initialise the TTCrx, the **enProm/PromReset** pin has to be connected to VDD with a pull-up resister. The pin is both input and output, using a similar technique as for reading the hardwired ID: When the TTCrx reset is active, the **enProm/PromReset** output driver is deactivated, allowing the pin to acquire the value of the resistor-connected voltage. At the falling edge of the internal reset line the value at the **enProm/PromReset** pin is latched internally, and the output driver is activated.

Note that in the case that no PROM is present the **enProm/PromReset** pin has to be connected to GND with a pull-down resistor.

### **PROM** Data format

As shown in Table 3 (Chapter 3), 10 eight-bit registers are initialised from the serial PROM. Hence, the first 80 bits are read by the TTCrx and have to be programmed. The data sequence goes from lower bits to higher bits and from PROM register address 0 to 9 (Table 3). Hence, the first bit of the PROM corresponds to bit 0 of register 0 (="Fine delay 1" register), the last ( $80^{th}$ ) bit corresponds to bit 7 of register 9 (= "Config 3 " register).

The Xilinx XC1736D PROM has to be programmed to use an active-high reset.

### Automatic Reset due to Watchdog circuit

The TTCrx incorporates a watchdog circuit which monitors whether the phase-locked loop (PLL) of the clock and data-recovery circuit is properly locked to the Biphase Mark input signal. If the chip finds out that no lock is achieved for a certain time, then an automatic reset is initiated. After a reset caused by the watchdog circuit, bit <4> of the Status register is set to one. The user thus has the possibility of knowing whether an automatic reset has occurred by reading the Status register over the I2C bus.

<sup>&</sup>lt;sup>6</sup> Serial PROM type XC1736D from Xilinx [5].

## **TTCrx Signals and Timing**

This chapter describes the TTCrx external signals and the most important timing relations among these signals.

### TTCrx EXTERNAL SIGNALS

Figure 10 TTCrx external signals overview

The TTCrx signals available to the user are represented in Figure 10. Note that the signals on some pins (enProm/PromReset, Dout<7:0>/ID<7:0>, SubAddr<7:0>/ID<15:8>) are defined differently during a reset (see Chapter 8). A description of the functionality of the individual signal pins is given next.

#### BCnt<11:0>

Counter output bus. This bus reflects the content of the bunch, event low or event high counter register, depending on the value of bits <1:0> of the control register, and the cycle of the trigger sequence (See Chapter 6). Its data type is validated by the

signals **BCntStr**, **EvCntHStr** and **EvCntLStr**. For electrical specifications, see Table 14 – I/O cell: IOF3.

#### **BCntRes**

Bunch counter reset signal. Indicates a bunch counter reset as a consequence of a broadcast command (See Chapter 5). As in the case of the **L1Accept** signal, deskewing is controlled by bits <3:0> in the coarse delay register and by the content of Fine delay 1 register. For electrical specifications, see Table 14 – I/O cell: OB33.

#### BCntStr

Bunch counter strobe. Indicates that a bunch number is present on the output BCnt<11:0> bus. See Chapter 6. For electrical specifications, see Table 14– I/O cell: OB33

#### Brcst<7:6>

Broadcast commands/data output bus. User defined part of a broadcast message. See Chapter 5. For electrical specifications, see Table 14– I/O cell: OB33.

#### Brcst<5:2>